# PCB DESIGN PERFECTION STARTS IN THE CAD LIBRARY PART 1 – THE 1608 (EIA 0603) CHIP COMPONENT

September 2010

### **ABSTRACT**

The CAD library is the starting point that affects every process from PCB layout through PCB manufacturing and assembly. There are dozens of things to consider when creating a CAD library that are often overlooked or not even considered that will directly affect the quality of the part placement, via fanout, trace routing, post processing, fabrication and assembly processes. Part 1 of this paper describes every aspect that should be considered when creating chip CAD library parts and the impact that each feature of the CAD library has in the PCB process.

Author:

Tom Hausherr EDA Library Product Manager Mentor Graphics Corp. tom\_hausherr@mentor.com

### INTRODUCTION:

This paper is Part 1 of a series that is intended as an introduction to creating a high quality CAD library. We will review the elements of each component family on Tom Hausherr's blog. We need to address questions like:

- Why do we snap the lands (pads) to a 0.1 mm grid?

- Why is the assembly outline different than the silkscreen outline?

- Why do we snap the via fanout to a 1 mm grid?

- Why is it important to use metric units when creating your CAD library?

- What is the IPC-7351B standard and why is it important?

All of the components and their related land patterns can be found in the free LP Viewer that you can download at www.mentor.com/go/lpwizard.

I will never forget my friend Wolfgang's description of a PCB design error: "A small error on an ugly PCB layout is a big deal, but the same exact error on a nice looking PCB layout is minor issue".

Every good PCB designer has the heart of an artist and the mind of a mathematician and each PCB design is a different piece of art with mechanical precision. A good PCB designer takes pride in their workmanship as they strive to make each new PCB layout more perfect than the last. After 35 years of laying out over 2,000 PCB designs I can say without any reservation that PCB design perfection starts in the CAD library.

One of the secrets of today is that 90% of all component manufacturers are providing their component package dimensions in metric units. Texas Instruments only provides metric units for all 982 of their component packages. TI is following the metric mandate by all world standards organizations and 99% of all world governments. So the CAD library should also be built using metric units. Using metric units for PCB design layout is the future, so you should transition to metric as soon as possible and quit wasting your time building an Imperial unit working environment. The longer you wait to transition the harder it

becomes. If you're a PCB design artist in search of perfection, this paper will clearly illustrate why metric units for PCB layout is vastly superior. Let's start with the IPC-7351B Standard.

#### IPC-7351B standard uses a 3-Tier CAD library system:

- 1. Least for cell phones and hand held devices

- 2. Nominal for controlled environment desktop

- 3. Most for Military and Medical applications

I will be using the Nominal environment for the examples.

There are three types of CAD library parts; Throughhole, Surface Mount or a combination of the two technologies. SMD and PTH CAD libraries are distinctively different but the same basic rules apply to both technologies, "snap" and "round-off" CAD library land (pad) shapes to 0.05 mm increments. We need to discuss why this is so important and pictures are worth 1,000 words. Also, trying to create a paper that goes through the entire list of standard component families can turn into a 100 page book really fast. I also want to hear your feedback on these very important issues. After all, we're talking about our favorite subject "PCB Design Perfection" and if it starts at the CAD library, we need an open forum for discussion.

I'm going to give you a sample of the subject in this paper and then start posting all the other data at <a href="http://blogs.mentor.com/tom-hausherr/">http://blogs.mentor.com/tom-hausherr/</a>.

Each component family will have a dedicated post.

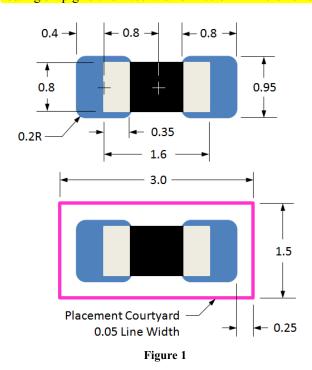

Chip components are the majority of the parts on a normal PCB layout. Chip components have a "Wraparound" lead form. The last PCB layout I did had 698 capacitors, 386 chip resistors and 81 chip inductors. The entire design had 1,250 parts and 1,165 or 93% were chip components. So it is very important that we address chip components first. The majority of chip components are metric by design. i.e.: 90% of all chip component dimensions are whole metric values. See Figure 1 for the dimensions of a standard 1608 (EIA 0603) component superimposed with its related land pattern and placement courtyard excess of 0.25 mm. Notice that the placement courtyard is 3.0 mm X 1.5 mm. This is perfect for placing this land pattern using a 0.5 mm grid system. They all line up perfectly.

The land size and centric placement are rounded in 0.05 mm increments to enhance trace routing using a 0.05 mm routing snap grid and trace widths in 0.25 mm increments.

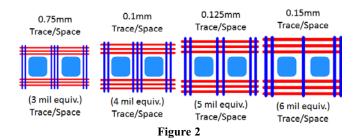

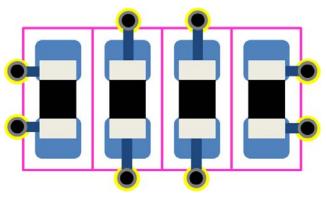

Figure 2 illustrates four of the most popular trace/space routing technologies that use a 0.05 mm routing grid. The 6 most popular metric trace widths rounded in 0.25 mm increments –

- 1. 0.075 mm (3 mils)

- 2. 0.1 mm (4 mils)

- 3. 0.125 mm (5 mils)

- 4. 0.15 mm (6 mils)

- 5. 0.2 mm (8 mils)

- 6. 0.25 mm (10 mils)

The main point that I am trying to make here is that using a PCB design grid system is best when using most CAD tools. One of the exceptions to this is the Expedition Enterprise CAD tool that handles gridless solutions effortlessly. But for everyone else in the industry, building CAD libraries, part placement, via fanout and trace routing using specific snap grids greatly enhances the speed and quality of the PCB layout.

The standard universal grid system to in 2010 is 0.05 mm but at times 0.025 mm increments need to be used specifically for trace/space rules.

The next generation of grid systems in the near future will be 0.01 mm, which I refer to as "high resolution". There will never be a need to go more than 2 places to the right of the decimal point for any PCB design feature values.

The same chip component technology can be applied to every chip resistor and capacitor used in the industry today. The most relevant aspect of this technology is that a 0.1 mm placement grid and a 0.05 mm routing grid system produces optimized results regardless of the trace/space technology because the land (pad) center snap grid is 0.05 mm from the origin and the land (pad) size round-off values are in 0.05mm increments.

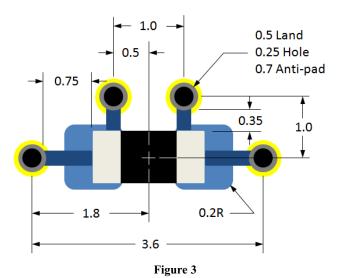

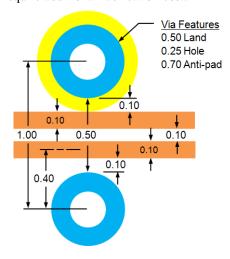

Let's talk about via fanout solutions for the same 1608 (EIA 0603) chip capacitor. In Figure 3 you can see 2 different fanout options and one is superior to the other. The fanout coming out the top has all the key features. The vias are 0.4 mm closer to the capacitor component terminals than the typical right/left fanout which decreases impedance and increases capacitance. Also, the top fanout vias snap to a 1 mm grid because the 1608 land pattern was snapped to a 0.5 mm grid system. The 0.5 mm via land (pad) diameter with 0.25 mm hole size and 0.7 mm plane anti-pad is perfect for 0.1 mm trace/space technology. See Figure 4 for the routing solutions. The trace width for the power fanout is 0.3 mm.

Figure 3 clearly illustrates the superior routing channels between two vias placed on a 1 mm snap grid. This same example can be used for all Chip and Molded Body Resistors and Capacitors. It is important to note that the plane anti-pad clearance does not infringe on the trace. The trace requires a clean uninterrupted return path on the adjacent reference plane. This via land, hole size and trace/space technology is very easy to manufacturer and does not require additional fabrication cost.

Figure 4

The part placement of the 1608 can use a 0.5 mm snap grid and the placement courtyards can be placed side by side. The via fanout can be a 1 mm snap grid when exiting the side of the land pattern, otherwise when exiting the top and bottom, a 0.1mm snap grid can be used.

Figure 5

See Figure 5 for the placement and fanout example for the 1608 chip components.

The IPC-7351B standard when a chip component size is less than 1.6 mm X 0.8 mm there are 7 rule changes that every PCB designer or CAD librarian must be aware of:

- 1. The Land (pad) snap grid changes from 0.1 mm to 0.02 mm

- 2. The land size round-off changes from 0.05 mm to 0.01 mm

- 3. The Toe goal changes from 0.35 mm to 0.2 mm

- 4. The corner radius changes from 0.2 mm to 0.15 mm

- The courtyard excess changes from 0.25 mm to 0.15 mm.

- 6. When entering the component min/max dimensions the "Nominal" Terminal dimensions are used for both the min & max fields

- 7. The part placement grid changes from 0.5 mm to 0.1 mm

Here are some basic guidelines and drafting recommendations for your Chip and Molded Body CAD library.

- Pad Spacing with DRC Checking and Pad Trimming when necessary

- a. Default Land to Land (inside to inside)

Clearance is 0.2 mm

- b. Default Silkscreen to Land Clearance is 0.25 mm

- 2. Four Outlines

- a. Silkscreen

- Silkscreen to exposed copper clearance setting defaults to 0.25 mm

- ii. Auto-trim feature to avoid exposed copper

- Outline size can be set to Nominal or Maximum component body

- iv. Line Width default is 0.2 mm

- v. Snap grid is 0.1 mm

- b. Assembly

- Outline size can be set to Nominal or Maximum component body

- ii. Line Width default is 0.1 mm

- iii. Snap grid is 0.1 mm

- Placement Courtyard adjustable sizing for IPC 3-Tier environment levels

- i. Default outline size is set to Maximum component body

- ii. Line Width default is 0.05 mm

- iii. Snap grid is 0.1 mm

- d. 3D Model Outline

- Default outline size is set to Maximum component body

- ii. Line Width default is 0.001 mm

- ii. Outline snaps to real maximum component outline (gridless)

- 3. Polarity Marking

- a. Silkscreen

- i. Default size is 0.5 mm minimum

- b. Assembly

- i. Default size is 1 mm minimum

- 4. Two Reference Designators with center/center justification (Ref Des Origin), right reading orthogonal, located at the land pattern origin with Height 1.5 mm and line width 10% of Height

- a. Silkscreen

- b. Assembly with automatic sizing for miniature parts (1005 & 0603)

- 5. IPC Zero Component Orientations

- a. 2-pin parts have Pin 1 on left

Go to http://blogs.mentor.com/tom-hausherr/ to read the remainder of this series of PCB Design Perfection Starts at the CAD Library. We're going to cover other Chip components and then Molded Body components and then SOT (Small Outline Transistor) component families next. I will elaborate on land pattern creation of all standard components.

## Visit the Mentor Graphics web site at www.mentor.com/go/lpwizard for the latest product information.

© 2010 Mentor Graphics Corporation. All Rights Reserved.

Mentor Graphics is a registered trademark of Mentor Graphics Corporation. All other trademarks are the property of their respective owners.

This document contains information that is proprietary to Mentor Graphics Corporation and may be duplicated in whole or in part by the original recipient for internal business purposed only, provided that this entire notice appears in all copies. In accepting this document, the recipient agrees to make every reasonable effort to prevent the unauthorized use of this information.

Corporate Headquarters Mentor Graphics Corporation 8005 S.W. Boeckman Road Wilsonville, Oregon 97070USA Phone: 503-685-7000 North American Support Center Phone: 800-547-4303 Silicon Valley

Mentor Graphics Corporation

1001 Ridder Park Drive

San Jose, California 95131 USA

Phone: 408-436-1500

Sales and Product Information

Phone: 800-547-3000

Europe Mentor Graphics Deutschland GmbH Arnulfstrasse 201 80634 Munich Germany Phone: +49.89.57096.0 Pacific Rim Mentor Graphics Taiwan Room 1001, 10F International Trade Building No. 333, Section 1, Keelung Road Taipei, Taiwan, ROC Phone: 886-2-27576020

Japan Mentor Graphics Japan Co., Ltd. Gotenyama Garden 7-35, Kita-Shinagawa 4-chome Shinagawa-Ku, Tokyo 140-0001 Japan

Phone: 81-3-5488-3033

LVG 9\_10

1028390-w